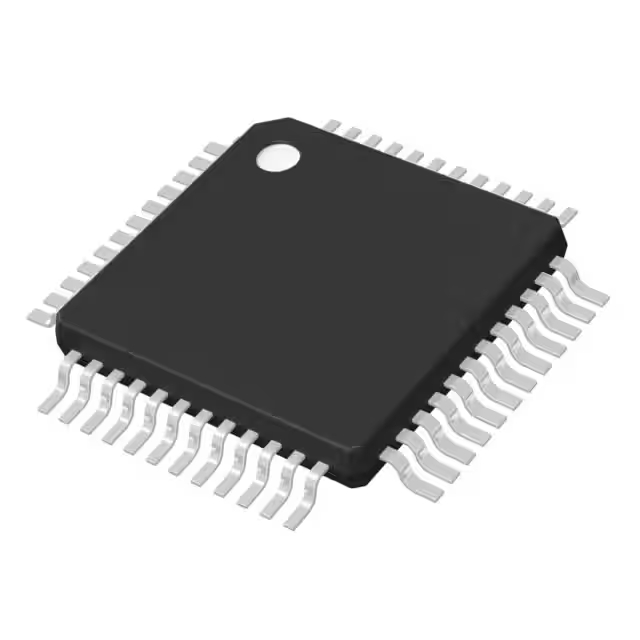

STM32F103C6T6A datasheet, pdf & pinout

- CoreProcessor: ARM® Cortex®-M3

- Core Size: 32-Bit Single-Core

- Peripherals: DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT

- Package: 48-LQFP

FREE delivery for orders over HK$250.00

Quick response, quick quotaton

Flash shipment,no worries after sales

Original channel,guarantee of the authentic products

STM32F103C6T6A Pinout

The STM32F103C6T6A is a 32-bit ARM Cortex-M3 microcontroller from STMicroelectronics, designed for high-performance embedded applications. Housed in a 48-pin LQFP package, it offers a wide range of peripherals, including multiple UARTs, SPIs, I2Cs, ADCs, and timers. The following table outlines the complete pin configuration, including power, ground, analog, digital I/O, and multifunction remappable pins essential for embedded hardware design and development.

| Pin | Pin Name | Type | I/O Level | Main Function | Default Function Description | Remap |

|---|---|---|---|---|---|---|

| 1 | VBAT | S | – | VBAT | – | – |

| 2 | PC13 | I/O | – | PC13 | TAMPER-RTC | – |

| 3 | PC14 | I/O | – | PC14 | OSC32_IN | – |

| 4 | PC15 | I/O | – | PC15 | OSC32_OUT | – |

| 5 | OSC_IN | I | – | OSC_IN | – | PD0(7) |

| 6 | OSC_OUT | O | – | OSC_OUT | – | PD1(7) |

| 7 | NRST | I/O | – | NRST | – | – |

| 8 | VSSA | S | – | VSSA | – | – |

| 9 | VDDA | S | – | VDDA | – | – |

| 10 | PA0 | I/O | – | PA0 | WKUP / USART2_CTS / ADC12_IN0 / TIM2_CH1_ETR(9) | – |

| 11 | PA1 | I/O | – | PA1 | USART2_RTS / ADC12_IN1 / TIM2_CH2(9) | – |

| 12 | PA2 | I/O | – | PA2 | USART2_TX / ADC12_IN2 / TIM2_CH3(9) | – |

| 13 | PA3 | I/O | – | PA3 | USART2_RX / ADC12_IN3 / TIM2_CH4(9) | – |

| 14 | PA4 | I/O | – | PA4 | SPI1_NSS(9) / USART2_CK / ADC12_IN4 | – |

| 15 | PA5 | I/O | – | PA5 | SPI1_SCK(9) / ADC12_IN5 | – |

| 16 | PA6 | I/O | – | PA6 | SPI1_MISO(9) / ADC12_IN6 / TIM3_CH1(9) | TIM1_BKIN |

| 17 | PA7 | I/O | – | PA7 | SPI1_MOSI(9) / ADC12_IN7 / TIM3_CH2(9) | TIM1_CH1N |

| 18 | PB0 | I/O | – | PB0 | ADC12_IN8 / TIM3_CH3(9) | TIM1_CH2N |

| 19 | PB1 | I/O | – | PB1 | ADC12_IN9 / TIM3_CH4(9) | TIM1_CH3N |

| 20 | PB2 | I/O | FT | PB2 / BOOT1 | – | – |

| 21 | PB10 | I/O | FT | PB10 | – | TIM2_CH3 |

| 22 | PB11 | I/O | FT | PB11 | – | TIM2_CH4 |

| 23 | VSS_1 | S | – | VSS_1 | – | – |

| 24 | VDD_1 | S | – | VDD_1 | – | – |

| 25 | PB12 | I/O | FT | PB12 | TIM1_BKIN(9) | – |

| 26 | PB13 | I/O | FT | PB13 | TIM1_CH1N(9) | – |

| 27 | PB14 | I/O | FT | PB14 | TIM1_CH2N(9) | – |

| 28 | PB15 | I/O | FT | PB15 | TIM1_CH3N(9) | – |

| 29 | PA8 | I/O | FT | PA8 | USART1_CK / TIM1_CH1 / MCO | – |

| 30 | PA9 | I/O | FT | PA9 | USART1_TX(9) / TIM1_CH2(9) | – |

| 31 | PA10 | I/O | FT | PA10 | USART1_RX(9) / TIM1_CH3 | – |

| 32 | PA11 | I/O | FT | PA11 | USART1_CTS / CAN_RX(9) / TIM1_CH4 / USBDM | – |

| 33 | PA12 | I/O | FT | PA12 | USART1_RTS / CAN_TX(9) / TIM1_ETR / USBDP | – |

| 34 | PA13 | I/O | FT | JTMS / SWDIO | – | PA13 |

| 35 | VSS_2 | S | – | VSS_2 | – | – |

| 36 | VDD_2 | S | – | VDD_2 | – | – |

| 37 | PA14 | I/O | FT | JTCK / SWCLK | – | PA14 |

| 38 | PA15 | I/O | FT | JTDI | – | TIM2_CH1_ETR / PA15 / SPI1_NSS |

| 39 | PB3 | I/O | FT | JTDO | – | TIM2_CH2 / PB3 / TRACESWO |

| 40 | PB4 | I/O | FT | NJTRST | – | TIM3_CH1 / PB4 / SPI1_MISO |

| 41 | PB5 | I/O | – | PB5 | I2C1_SMBA | TIM3_CH2 / SPI1_MOSI |

| 42 | PB6 | I/O | FT | PB6 | I2C1_SCL(9) | USART1_TX |

| 43 | PB7 | I/O | FT | PB7 | I2C1_SDA(9) | USART1_RX |

| 44 | BOOT0 | I | – | BOOT0 | – | – |

| 45 | PB8 | I/O | FT | PB8 | – | I2C1_SCL / CAN_RX |

| 46 | PB9 | I/O | FT | PB9 | – | I2C1_SDA / CAN_TX |

| 47 | VSS_3 | S | – | VSS_3 | – | – |

| 48 | VDD_3 | S | – | VDD_3 | – | – |

This comprehensive pinout table ensures accurate and efficient hardware interfacing with the STM32F103C6T6A. Whether you’re designing a communication module, implementing motor control, or integrating USB or CAN peripherals, understanding each pin’s capabilities—including alternate functions and remap options—is crucial for optimizing your circuit layout and achieving reliable system performance.

.JPG)