ADRF5730BCCZN データシート、価格 | pdf

- 減衰値: 0.5dB~31.5dB

- 周波数範囲: 100MHz~40GHz

- 電力(ワット): 500mW

- パッケージ: ストリップ

HK$250.00以上のご注文で送料無料

迅速な対応、迅速な見積もり

すぐに発送、アフターサービスも安心

オリジナルチャネル、本物の製品の保証

ADRF5730BCCZN-R7 データシート

スペイン語のPDFをダウンロード: ADRF5730BCCZN データシート PDF

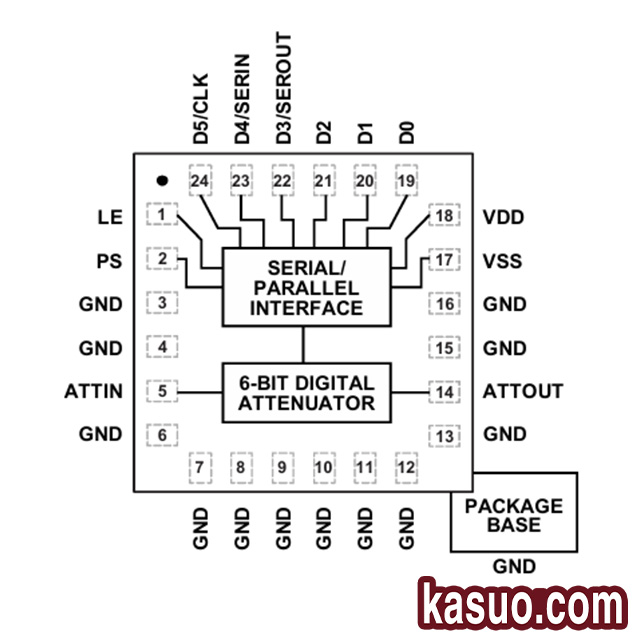

ADRF5730BCCZN ピン配置等価回路

adrf5730bccznは、アナログ・デバイセズ社の6ビット・シリコン・デジタル・アッテネータで、0.5dBステップで31.5dBの減衰量制御が可能です。このチップは100MHz~40GHzの周波数範囲で動作し、4.8dB未満の挿入損失と優れた減衰精度を実現します。ポート設計には、従来の50Ω特性インピーダンス整合を採用しています。広帯域アプリケーションでは、RF伝送信号ラインのインピーダンス整合により、高周波における信号エネルギー損失をさらに低減できます。また、外部デバイスとの通信にSPIインターフェースを備えています。

ピンの定義:

| ピン | 名前 | 関数 |

|---|---|---|

| 1 | ル | ロック有効入力。 |

| 2 | 追伸 | パラレルまたはシリアル制御インターフェースの入力を選択します。 |

| 3、4、6~13、15、16 | GND | 接地ピン。 |

| 5 | アティン | 減衰器入力。このピンは0VにDC結合されており、ACインピーダンスは50Ωです。 |

| 14 | アトゥー | 減衰器出力。このピンは0VにDC結合されており、ACインピーダンスは50Ωです。 |

| 17 | VSS | 負電源入力。 |

| 18 | VDD | 正電源入力。 |

| 19 | D0 | 0.5 dB 減衰ビットを備えたパラレル制御入力。 |

| 20 | D1 | 1 dB 減衰器ビットのパラレル制御。 |

| 21 | D2 | 2 dB 減衰器ビットのパラレル制御入力。 |

| 22 | D3/セロウト | 4 dB 減衰器ビットのパラレル制御入力 (D3) またはシリアル データ出力 (SEROUT)。 |

| 23 | D4/セリン | 8 dB 減衰器ビットのパラレル制御入力 (D4) またはシリアル データ入力 (SERIN)。 |

| 24 | D5/CLK | 16 dB 減衰器ビットパラレル制御入力 (D5) またはシリアル クロック入力 (CLK)。 |

| EPAD | ボンディングパッド | 露出したはんだパッドは DC グランドに接続する必要があります。 |

代替モデルオプション

実際のアプリケーションでは、何らかの理由でADRF5730BCCZNの代替選択を見つける必要がある場合がありますが、検索した後、完全に適切な製品はADRF5730BCCZNに完全に準拠しているだけである可能性があることがわかります。そのため、代替モデルを選択する際には、上位代替選択や下位代替選択などの類似製品に焦点を当てます。選択によって置き換えられていないことが一般的に確実であり、下位代替選択がまだ選択されていない場合は、精度または領域の一部が失われる可能性があります。全体として、トレードオフを行う必要があります。選択時に考慮すべき主なパラメータは、1.動作周波数範囲、2.電源と制御信号の互換性、3.減衰範囲、および4.パッケージが要件を満たしているかどうかです。ここでは、いくつかの代替代替品を紹介します。

| 写真 | 名前 | 周波数範囲 | 整合インピーダンス | 減衰 | パッケージ |

|---|---|---|---|---|---|

|

ADRF5716 | 0.1GHz~30GHz | 50Ω | 16dB~48dB | VFLGA-20-EP |

|

ADRF5730 | 100MHz~40GHz | 50Ω | 0.5dB~31.5dB | VFLGA-24-EP |

|

ADRF5731 | 100MHz~40GHz | 50Ω | 2dB~30dB | VFLGA-16-EP |

|

ADRF5740BCCZN-R7 | 10MHz~60GHz | 50Ω | 2dB~22dB | VFLGA-16-EP |

代表的な用途

現代のラジオ受信業界の設計において、RFサンプリング構造は非常に重要であり、アーキテクチャの選択はシステムの高調波性能に大きな影響を与えます。主な方法には、直接RFサンプリングとヘテロダインコンバータの2つがあります。直接RFサンプリングと比較したヘテロダインアーキテクチャの欠点は、構造が複雑で、高調波が発生しやすく、正確な設計周波数計画が必要であり、複雑な構造は高コストにもつながることです。そのため、現在はRF構造がより一般的に使用されています。図は比較的単純なRF構造を示しています。RF信号は入力ポートから受信され、次に信号は増幅器によって増幅され、フィルタに入って帯域選択とクラッター抑制が完了します(増幅とフィルタリングにより信号品質が効果的に向上します)。最後にRF信号はアナログ/デジタルコンバータ(ADC)によって受信されます。