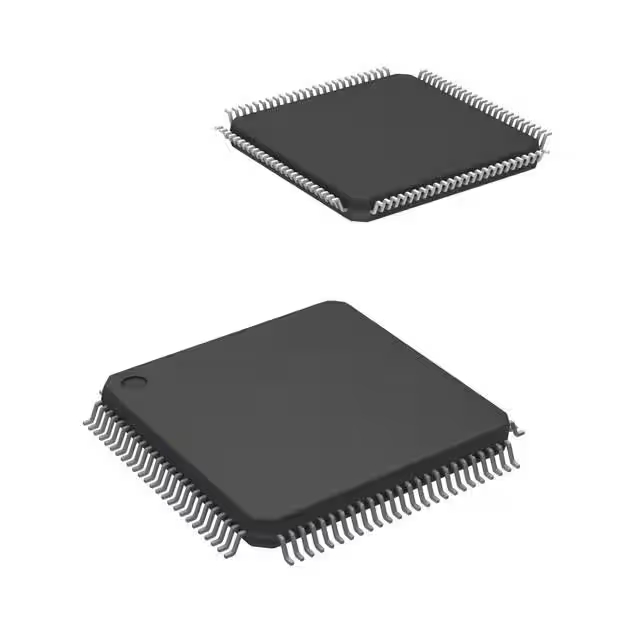

AD9858BSVZ データシートと価格情報

- 解像度(ビット): 10b

- マスターフクロック: 1GHz

- チューニングワード幅(ビット): 32 b

- パッケージ: 100-TQFP露出パッド

HK$250.00以上のご注文で送料無料

迅速な対応、迅速な見積もり

すぐに発送、アフターサービスも安心

オリジナルチャネル、本物の製品の保証

AD9858BSVZ Analog Devices Datasheet-INGKECHIPS.COM

日本語PDFをダウンロード: AD9858BSVZ データシート PDF

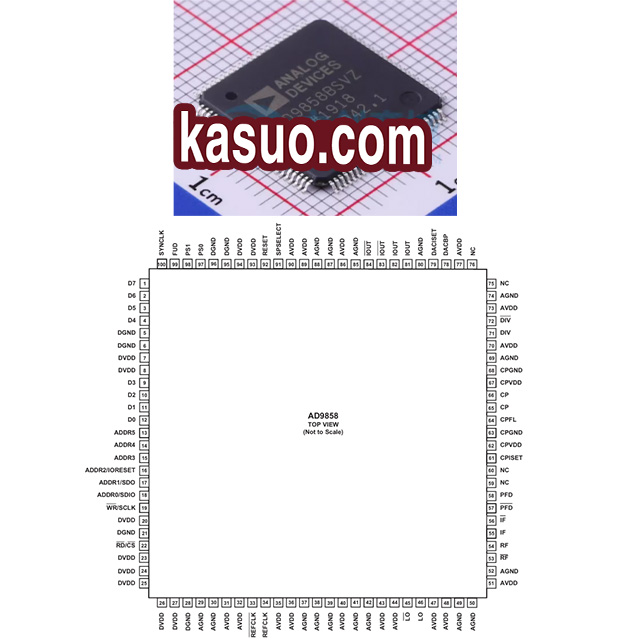

AD9858BSVZピン配置等価回路

AD9858BSVZは、アナログ・デバイセズの1GSPSダイレクト・デジタル・シンセサイザ・チップです。高解像度、高速周波数スイッチング、低位相ノイズといった利点を備え、新世代周波数シンセサイザの代表的製品の一つです。10ビット高速デジタル/アナログ・コンバータ(DAC)、位相アキュムレータ、正弦波ルックアップテーブル、プログラマブル周波数レジスタを統合し、完全なDDSを構成しています。また、システムクロックを逓倍して出力周波数範囲を拡大するオンチップ位相ロックループ(PLL)も搭載しています。

AD9858BSVZ は、最大 1 GSPS の内部クロック速度、内部 PLL 乗算器による最大 2GHz のシステム クロック周波数、優れた位相ノイズと SFDR、最大 48 ビットの周波数スケーリング分解能、および低消費電力 (標準 2W) を備えており、ほとんどの高精度周波数合成ニーズを満たします。

ピンの定義:

| ピン番号 | ニモニック | 入出力 | 説明 |

|---|---|---|---|

| 1~4、9~12 | D7からD0 | 私 | パラレルポートデータ。これらのピンの機能は、I/O ポートがパラレルポートとして設定されている場合にのみ有効です。 |

| 5, 6, 21, 28, 95, 96 | DGND | デジタルグラウンド。 | |

| 7、8、20、23~27、93、94 | DVDD | デジタル電源電圧。 | |

| 13~18歳 | ADDR5からADDR0 | 私 | I/O ポートがパラレル ポートとして設定されている場合、これらのピンはオンチップ レジスタにアクセスするための 6 ビット アドレス選択として機能します (シリアル ポート モードについては、IORESET、SDO、および SDIO ピンを参照してください)。 |

| 16 | IORESET | 私 | シリアルプログラミングモードのみ有効です。シリアルI/Oバスコントローラをリセットします。不適切なプログラミングプロトコルが原因でシリアルバスが応答しなくなった場合の回復に使用されます。 |

| 17 | SDO | お | シリアルプログラミングモードのみ有効です。3線式モードでは単方向シリアルデータ出力です。2線式モードでは未使用です。 |

| 18 | SDIO | 入出力 | シリアルプログラミングモードのみ有効です。3線式モードではシリアルデータ入力、2線式モードでは双方向シリアルデータピンです。 |

| 19 | WR/SCLK | 私 | パラレルモードの場合:アクティブロー書き込みパルス(WR)。シリアルモードの場合:シリアルデータクロック(SCLK)。 |

| 22 | RD/CS | 私 | パラレルモードの場合:アクティブローの読み取りパルス(RD)。シリアルモードの場合:デバイス選択用のアクティブローのチップセレクト(CS)。 |

| 29、30、37~39、41、42、49、50、52、69、74、80、85、87、88 | AGND | 私 | アナロググラウンド。 |

| 31, 32, 35, 36, 40, 43, 44, 47, 48, 51, 70, 73, 77, 86, 89, 90 | AVDD | 私 | アナログ電源電圧。 |

| 33 | REFCLK | 私 | リファレンスクロック相補入力。REFCLKポートがシングルエンドモードで動作する場合、REFCLKは0.1µFのコンデンサを使用してAVDDにデカップリングする必要があります。 |

| 34 | REFCLK | 私 | リファレンスクロック入力。 |

| 45 | LO | 私 | ミキサー局部発振器(LO)相補入力。LOポートがシングルエンドモードで動作する場合、LOは0.1µFのコンデンサでAVDDにデカップリングする必要があります。 |

| 46 | LO | 私 | ミキサー局部発振器 (LO) 入力。 |

| 53 | 高周波 | 私 | アナログミキサーRF相補入力。RFポートがシングルエンドモードで動作する場合、RFは0.1µFのコンデンサでAVDDにデカップリングする必要があります。 |

| 54 | 高周波 | 私 | アナログ ミキサー RF 入力。 |

| 55 | もし | お | アナログミキサー IF 出力。 |

| 56 | もし | お | アナログ ミキサー IF コンプリメンタリ出力。 |

| 57 | 救命胴衣 | 私 | 位相周波数検出器の相補入力。PFDポートがシングルエンドモードで動作する場合、PFDは0.1µFのコンデンサでAVDDにデカップリングする必要があります。 |

| 58 | 救命胴衣 | 私 | 位相周波数検出器入力。 |

| 59, 60, 75, 76 | ノースカロライナ州 | 接続がありません。 | |

| 61 | CPISET | 私 | チャージポンプ出力電流制御。CPISETからCPGNDに接続された抵抗によって、チャージポンプの基準電流が確立されます。 |

| 62, 67 | CPVDD | 私 | チャージポンプ供給電圧。 |

| 63, 68 | CPGND | 私 | チャージポンプのグランド。 |

| 64 | CPFL | お | チャージ ポンプの高速ロック出力。 |

| 65, 66 | CP | お | チャージポンプ出力。 |

| 71 | 部門 | 私 | 位相周波数検出器のフィードバック入力。 |

| 72 | 部門 | 私 | 位相周波数検出器フィードバック相補入力。DIVポートがシングルエンドモードで動作する場合、DIVは0.1µFのコンデンサでAVDDにデカップリングする必要があります。 |

| 78 | DACBP | DACベースラインデカップリングピン。通常は0.1µFのコンデンサでピン77にバイパスされます。 | |

| 79 | ダシセット | 私 | DACISET から AGND に接続された抵抗器は、DAC の基準電流を確立します。 |

| 81, 82 | IOUT | お | DAC出力。 |

| 83, 84 | IOUT | お | DAC 補完出力。 |

| 91 | SPSELECT | 私 | I/O ポート シリアル/パラレル プログラミング モード選択ピン。ロジック 0 はシリアル プログラミング モード、ロジック 1 はパラレル プログラミング モードです。 |

| 92 | リセット | 私 | アクティブハイのハードウェアリセットピン。RESETピンをアサートすると、AD9858はデフォルトの動作状態に強制されます。 |

| 97, 98 | PS0、PS1 | 私 | 4つの内部プロファイルのいずれかを選択するために使用されます。これらのピンはSYNCLK出力に同期しています。 |

| 99 | FUD | 私 | 周波数更新。立ち上がりエッジで内部バッファレジスタの内容をメモリレジスタに転送します。このピンはSYNCLK出力に同期しています。 |

| 100 | シンクルク / EPAD | お | クロック出力ピン。外部ハードウェアの同期回路として機能します。SYNCLKはREFCLK/8で動作します。露出パドルはグランドに半田付けする必要があります。 |

代替モデルオプション:

AD9858BSVZと同一かつ機能的に同等の代替品は稀であるため、選定プロセスにおいては、類似機能または一貫性のあるパッケージを備えたデバイスに重点を置いています。これらの代替品は、周波数分解能、消費電力レベル、制御インターフェースの種類、パッケージ形式において部分的に類似していますが、完全なピン互換性や機能の一貫性は備えていません。以下の代替品選定の提案は、「機能的に部分的に互換性がある」という原則に基づいています。

| 写真 | 名前 | 動作電圧 | 最高システムクロック周波数 | 周波数分解能 | パッケージ |

|---|---|---|---|---|---|

|

AD9957BSVZ-リール | 1.8V~3.3V | 1GHz | 14 | TQFP-100-EP (14×14) |

|

AD9910BSVZ-リール | 1.8V~3.3V | 1GHz | 14 | TQFP-100-EP (14×14) |

|

CBM99D57BQ | 1.8V~3.3V | 1GHz | 14 | TQFP-100-EP (14×14) |

|

CBM99D10BQ | 1.8V~3.3V | 1GHz | 14 | TQFP-100-EP (14×14) |

主な用途:

図はDDSベースの可変周波数ループ発振器を示しており、デジタル制御により高精度の周波数信号を実現します。具体的なプロセスは次のとおりです。入力はまず1GSPS DDSモジュールに入り、高解像度のデジタル信号を生成します。次に、2つのチャネルに分割されます。1つはDACを介してアナログ信号に直接変換され、DC-400MHzローパスフィルタによって除去されます。もう1つは周波数分周器によって生成され、固定ループLO1が生成され、安定した2GHz局部発振信号が提供され、ミキシング精度が確保されます。その後、信号はPLLループに入り、プログラマブル分周器(÷2/÷4)によって周波数が低減され、150MHz位相検出器で基準周波数と比較されます。生成された誤差信号はチャージポンプ(0.5mA〜2mA調整可能)とループフィルタによって安定した電圧に変換され、VCOが制御されて2GHz±150MHzの発振信号が出力されます。このシステムは、DDS の高解像度と PLL の安定性を組み合わせることで、広範囲にわたる周波数合成と低位相ノイズをサポートしており、通信システム、レーダー、テスト機器など、周波数精度が重要となるシナリオに適しています。