ADRF5730BCCZN Ficha técnica, precio | PDF

- Marcas: Dispositivos analógicos Inc.

- Descargar: Hoja de datos del ADRF5730BCCZN (PDF)

- Precio: consulta

- En stock: 11,885

- Valor de atenuación: 0,5 dB ~ 31,5 dB

- Rango de frecuencia: 100 MHz ~ 40 GHz

- Potencia (vatios): 500 mW

- Paquete: Banda

Envío GRATUITO para pedidos superiores a HK$250.00

Respuesta rápida, cotización rápida.

Envío rápido, sin preocupaciones posventa.

Canal original, garantía de los productos auténticos.

ADRF5730BCCZN-R7 Datasheet

Descargar PDF en español: Hoja de datos del ADRF5730BCCZN (PDF)

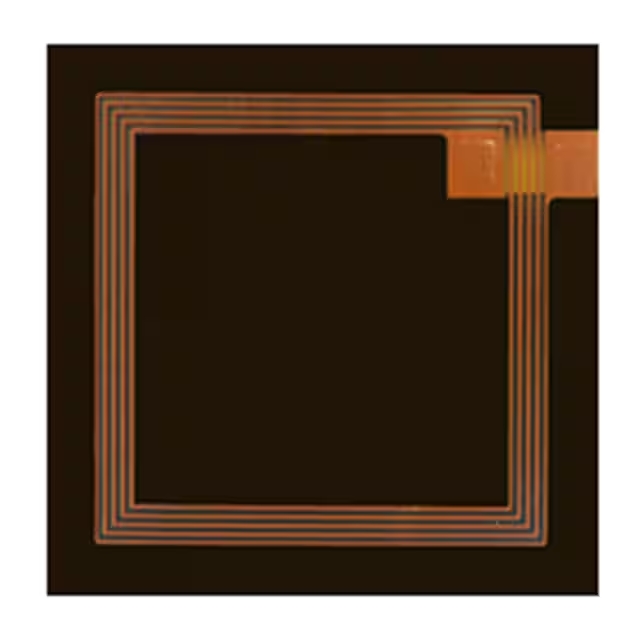

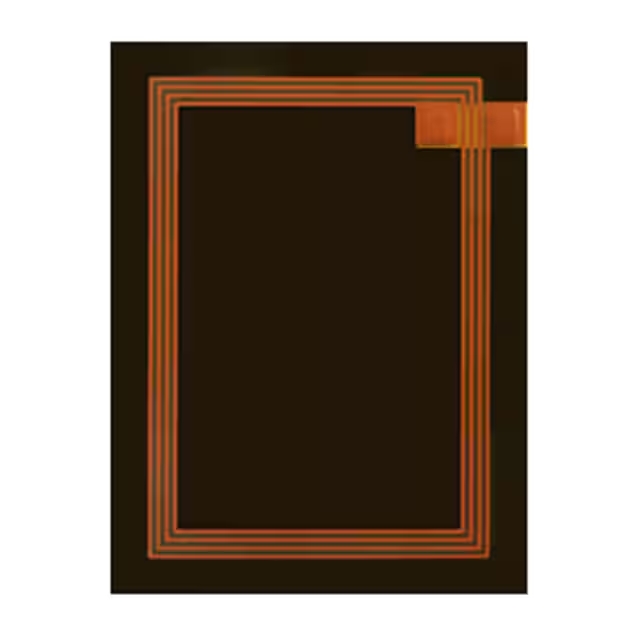

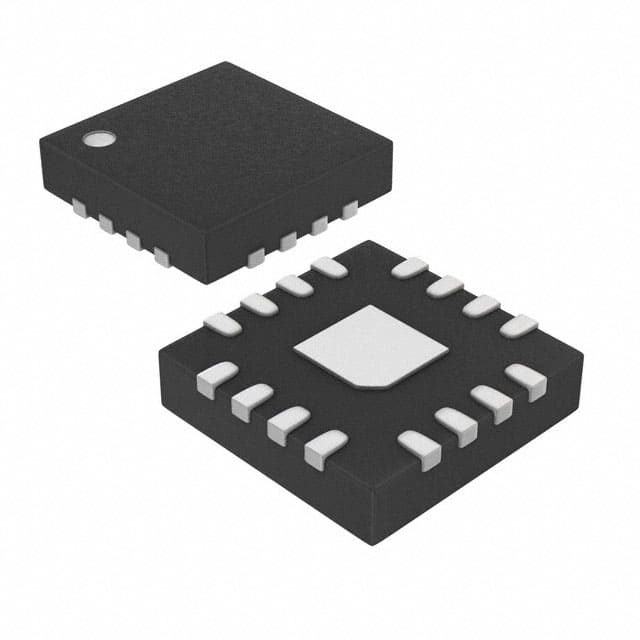

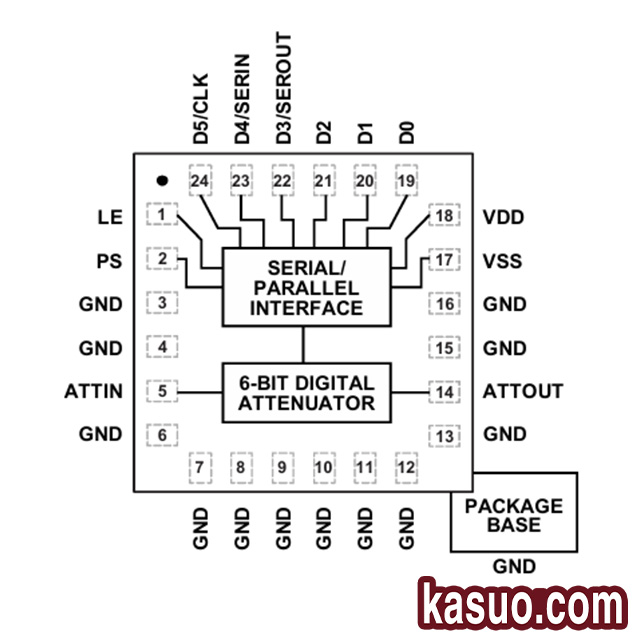

Circuito equivalente de distribución de pines ADRF5730BCCZN

El adrf5730bcczn es un atenuador digital de silicio de 6 bits de Analog Devices que proporciona un control de atenuación de 31,5 dB en pasos de 0,5 dB. El chip puede operar en un rango de frecuencia de 100 MHz a 40 GHz y ofrece una pérdida de inserción superior a 4,8 dB y una excelente precisión de atenuación. El diseño del puerto utiliza una adaptación de impedancia característica convencional de 50 Ω. Para aplicaciones de banda ancha, la adaptación de impedancia en la línea de señal de transmisión de RF puede reducir aún más la pérdida de energía de la señal a altas frecuencias. Además, puede proporcionar una interfaz SPI para la comunicación con dispositivos externos.

Definición de pin:

| ALFILER | NOMBRE | FUNCIÓN |

|---|---|---|

| 1 | LE | Habilitar entrada de bloqueo. |

| 2 | PD | Seleccione la entrada para la interfaz de control paralela o serial. |

| 3, 4, 6–13, 15, 16 | Tierra | Pin de puesta a tierra. |

| 5 | ATENCIÓN | Entrada del atenuador. Este pin está conectado a CC a 0 V y tiene una impedancia de CA de 50 Ω. |

| 14 | ATENCIÓN | Salida del atenuador. Este pin está conectado a CC a 0 V y tiene una impedancia de CA de 50 Ω. |

| 17 | VSS | Entrada de potencia negativa. |

| 18 | VDD | Entrada de potencia positiva. |

| 19 | D0 | Entrada de control paralelo con bit atenuador de 0,5 dB. |

| 20 | D1 | Control paralelo de bits del atenuador de 1 dB. |

| 21 | D2 | Entrada de control paralelo para bits de atenuación de 2 dB. |

| 22 | D3/SEROUT | Entrada de control paralelo de bits de atenuación de 4 dB (D3) o salida de datos en serie (SEROUT). |

| 23 | D4/SERÍN | Entrada de control en paralelo de bits de atenuación de 8 dB (D4) o entrada de datos en serie (SERIN). |

| 24 | D5/CLK | Entrada de control paralelo de bits de atenuación de 16 dB (D5) o entrada de reloj en serie (CLK). |

| EPAD | almohadilla de unión | La almohadilla de soldadura expuesta debe estar conectada a tierra de CC. |

Opciones de modelos alternativos

En aplicaciones prácticas, puede ser necesario buscar una alternativa al ADRF5730BCCZN por diversas razones. Sin embargo, tras la búsqueda, se observa que un producto completamente compatible solo puede ser totalmente compatible con el ADRF5730BCCZN. Por lo tanto, al seleccionar modelos alternativos, nos centramos en productos similares, como la selección de sustitución superior o inferior. Generalmente, es seguro que no se ha reemplazado por la selección, y parte de la precisión o el área pueden perderse si aún no se selecciona la selección de sustitución subordinada. En resumen, es necesario llegar a un acuerdo. Los principales parámetros a considerar en la selección son: 1. el rango de frecuencia de trabajo, 2. la compatibilidad de la fuente de alimentación y la señal de control, 3. el rango de atenuación, y 4. si el encapsulado cumple con los requisitos. A continuación, se presentan algunas alternativas de reemplazo.

| Imagen | Nombre | Rango de frecuencia | Impedancia de adaptación | Atenuación | Paquete |

|---|---|---|---|---|---|

|

ADRF5716 | 0,1 GHz ~ 30 GHz | 50 Ω | 16 dB ~ 48 dB | VFLGA-20-EP |

|

ADRF5730 | 100 MHz ~ 40 GHz | 50 Ω | 0,5 dB ~ 31,5 dB | VFLGA-24-EP |

|

ADRF5731 | 100 MHz ~ 40 GHz | 50 Ω | 2dB~30dB | VFLGA-16-EP |

|

ADRF5740BCCZN-R7 | 10 MHz ~ 60 GHz | 50 Ω | 2dB~22dB | VFLGA-16-EP |

Aplicaciones típicas

La estructura de muestreo de RF es fundamental en el diseño de la industria moderna de recepción de radio, y la elección de la arquitectura influye considerablemente en el rendimiento armónico del sistema. Existen dos métodos principales: muestreo directo de RF y conversor heterodino. Las desventajas de la arquitectura heterodina, en comparación con el muestreo directo de RF, son su complejidad, la fácil generación de armónicos, la necesidad de una planificación precisa de la frecuencia de diseño y su elevado coste. Por lo tanto, la estructura de RF es la más utilizada actualmente. El diagrama muestra una estructura de RF relativamente sencilla: la señal de RF se recibe a través del puerto de entrada, se amplifica mediante un amplificador y entra en un filtro para completar la selección de banda y la supresión de interferencias (la amplificación y el filtrado mejoran eficazmente la calidad de la señal); finalmente, la señal de RF es recibida por un conversor analógico-digital (ADC).