AD9858BSVZ Datenblatt und Preisinformationen

- Auflösung (Bits): 10 b

- Masterfclk: 1 GHz

- Wortbreite (Bits) anpassen: 32 b

- Paket: 100-TQFP freiliegendes Pad

KOSTENLOSE Lieferung für Bestellungen über HK$250.00

Schnelle Reaktion, schnelles Angebot

Blitzversand, keine Sorgen nach dem Verkauf

Originalkanal, Garantie der authentischen Produkte

AD9858BSVZ Analog Devices Datenblatt-INGKECHIPS.COM

Japanisches PDF herunterladen: AD9858BSVZ Datenblatt PDF

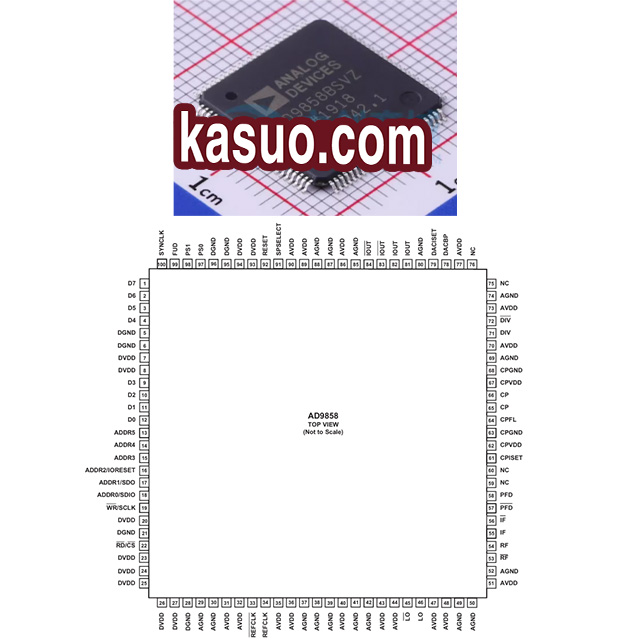

AD9858BSVZ Pinbelegung Ersatzschaltbild

AD9858BSVZ ist ein 1 GSPS direkter digitaler Synthesizer-Chip von Analog Devices, der die Vorteile hoher Auflösung, schneller Frequenzumschaltung und geringem Phasenrauschen bietet und zu den repräsentativen Produkten der neuen Generation von Frequenzsynthesizern zählt. Er integriert einen 10-Bit-Hochgeschwindigkeits-Digital-Analog-Wandler (DAC), einen Phasenakkumulator, eine Sinuswellen-Lookup-Tabelle und programmierbare Frequenzregister zu einem vollständigen DDS sowie einen integrierten Phasenregelkreis (PLL), der den Systemtakt multipliziert und den Ausgangsfrequenzbereich erweitert.

AD9858BSVZ Mit internen Taktgeschwindigkeiten von bis zu 1 GSPS, Systemtaktfrequenzen von bis zu 2 GHz mit internen PLL-Multiplikatoren, ausgezeichnetem Phasenrauschen und SFDR, Frequenzskalierungsauflösung von bis zu 48 Bit und geringem Stromverbrauch (typischerweise 2 W), um die überwiegende Mehrheit der Anforderungen an eine hochpräzise Frequenzsynthese zu erfüllen.

Pin-Definition:

| Pin-Nr. | Mnemonische | E/A | Beschreibung |

|---|---|---|---|

| 1 bis 4, 9 bis 12 | D7 bis D0 | ICH | Daten des Parallelports. Die Funktionalität dieser Pins ist nur gültig, wenn der E/A-Port als Parallelport konfiguriert ist. |

| 5, 6, 21, 28, 95, 96 | DGND | Digitaler Boden. | |

| 7, 8, 20, 23 bis 27, 93, 94 | DVDD | Digitale Versorgungsspannung. | |

| 13 bis 18 | ADDR5 bis ADDR0 | ICH | Wenn der E/A-Port als Parallelport konfiguriert ist, dienen diese Pins als 6-Bit-Adressauswahl für den Zugriff auf die On-Chip-Register (siehe die Pins IORESET, SDO und SDIO für den seriellen Portmodus). |

| 16 | IORESET | ICH | Gilt nur für den seriellen Programmiermodus. Setzt den seriellen E/A-Bus-Controller zurück. Wird zur Wiederherstellung verwendet, wenn der serielle Bus aufgrund eines fehlerhaften Programmierprotokolls nicht reagiert. |

| 17 | SDO | O | Gilt nur für den seriellen Programmiermodus. Im 3-Draht-Modus ist dies ein unidirektionaler serieller Datenausgang. Im 2-Draht-Modus unbenutzt. |

| 18 | SDIO | E/A | Gilt nur für den seriellen Programmiermodus. Im 3-Draht-Modus ist dies der serielle Dateneingang. Im 2-Draht-Modus ist es ein bidirektionaler serieller Datenpin. |

| 19 | WR/SCLK | ICH | Im Parallelmodus: aktiver Low-Schreibimpuls (WR). Im Serienmodus: serieller Datentakt (SCLK). |

| 22 | RD/CS | ICH | Im Parallelmodus: Active Low-Leseimpuls (RD). Im Serienmodus: Active Low-Chip-Select (CS) zur Geräteauswahl. |

| 29, 30, 37 bis 39, 41, 42, 49, 50, 52, 69, 74, 80, 85, 87, 88 | AGND | ICH | Analoge Masse. |

| 31, 32, 35, 36, 40, 43, 44, 47, 48, 51, 70, 73, 77, 86, 89, 90 | AVDD | ICH | Analoge Versorgungsspannung. |

| 33 | REFCLK | ICH | Komplementärer Referenztakteingang. Wenn der REFCLK-Port im Single-Ended-Modus arbeitet, sollte REFCLK mit einem 0,1-µF-Kondensator von AVDD entkoppelt werden. |

| 34 | REFCLK | ICH | Referenztakteingang. |

| 45 | LO | ICH | Komplementärer Eingang des Mischer-Lokaloszillators (LO). Wenn der LO-Port im Single-Ended-Modus arbeitet, sollte LO mit einem 0,1-µF-Kondensator von AVDD entkoppelt werden. |

| 46 | LO | ICH | Eingang des lokalen Oszillators (LO) des Mischers. |

| 53 | RF | ICH | Komplementärer HF-Eingang des analogen Mischers. Wenn der HF-Anschluss im Single-Ended-Modus arbeitet, sollte die HF-Verbindung mit einem 0,1-µF-Kondensator zum AVDD entkoppelt werden. |

| 54 | RF | ICH | Analoger Mischer-HF-Eingang. |

| 55 | WENN | O | Analoger Mischer-ZF-Ausgang. |

| 56 | WENN | O | Komplementärer ZF-Ausgang des analogen Mischers. |

| 57 | Rettungsweste | ICH | Komplementärer Eingang des Phasenfrequenzdetektors. Wenn der PFD-Anschluss im Single-Ended-Modus arbeitet, sollte PFD mit einem 0,1-µF-Kondensator von AVDD entkoppelt werden. |

| 58 | Rettungsweste | ICH | Eingang für Phasenfrequenzdetektor. |

| 59, 60, 75, 76 | NC | Keine Verbindung. | |

| 61 | CPISET | ICH | Steuerung des Ausgangsstroms der Ladungspumpe. Ein von CPISET an CPGND angeschlossener Widerstand legt den Referenzstrom für die Ladungspumpe fest. |

| 62, 67 | CPVDD | ICH | Versorgungsspannung der Ladepumpe. |

| 63, 68 | CPGND | ICH | Masse der Ladungspumpe. |

| 64 | CPFL | O | Schnellverriegelungsausgang der Ladepumpe. |

| 65, 66 | CP | O | Ausgang der Ladungspumpe. |

| 71 | DIV | ICH | Rückkopplungseingang des Phasenfrequenzdetektors. |

| 72 | DIV | ICH | Komplementärer Eingang zur Rückkopplung des Phasenfrequenzdetektors. Wenn der DIV-Port im Single-Ended-Modus arbeitet, sollte DIV mit einem 0,1-µF-Kondensator von AVDD entkoppelt werden. |

| 78 | DACBP | DAC-Basislinien-Entkopplungspin. Normalerweise mit einem 0,1-µF-Kondensator auf Pin 77 umgangen. | |

| 79 | DACISET | ICH | Ein von DACISET an AGND angeschlossener Widerstand legt den Referenzstrom für den DAC fest. |

| 81, 82 | IOUT | O | DAC-Ausgang. |

| 83, 84 | IOUT | O | Komplementärer DAC-Ausgang. |

| 91 | SPSELECT | ICH | Auswahlpin für den seriellen/parallelen Programmiermodus des E/A-Ports. Logik 0 ist der serielle Programmiermodus und Logik 1 ist der parallele Programmiermodus. |

| 92 | ZURÜCKSETZEN | ICH | Aktiver High-Hardware-Reset-Pin. Durch Aktivieren des RESET-Pins wird der AD9858 in seinen Standardbetriebszustand zurückversetzt. |

| 97, 98 | PS0, PS1 | ICH | Dient zur Auswahl eines der vier internen Profile. Diese Pins sind synchron zum SYNCLK-Ausgang. |

| 99 | FUD | ICH | Frequenzaktualisierung. Die steigende Flanke überträgt den Inhalt der internen Pufferregister in die Speicherregister. Dieser Pin ist synchron zum SYNCLK-Ausgang. |

| 100 | SYNCLK / EPAD | O | Taktausgangspin. Dient als Synchronisierer für externe Hardware. SYNCLK läuft bei REFCLK/8. Freiliegendes Paddle muss an Masse gelötet werden. |

Alternative Modelloptionen:

Identische und funktional gleichwertige Alternativen zum AD9858BSVZ sind selten. Daher konzentrieren wir uns bei der Auswahl stärker auf Geräte mit ähnlichen Funktionen oder identischen Gehäusen. Diese Alternativen ähneln sich teilweise hinsichtlich Frequenzauflösung, Stromverbrauch, Steuerschnittstellentypen und Gehäuseformaten, weisen jedoch keine vollständige Pin-Kompatibilität oder funktionale Konsistenz auf. Die folgenden Vorschläge zur Auswahl alternativer Komponenten basieren auf dem Prinzip der „teilweise funktionskompatiblen“ Kompatibilität.

| Bild | Name | Betriebsspannung | Höchste Systemtaktfrequenz | Frequenzauflösung | Paket |

|---|---|---|---|---|---|

|

AD9957BSVZ-REEL | 1,8 V bis 3,3 V | 1 GHz | 14 | TQFP-100-EP (14×14) |

|

AD9910BSVZ-REEL | 1,8 V bis 3,3 V | 1 GHz | 14 | TQFP-100-EP (14×14) |

|

CBM99D57BQ | 1,8 V bis 3,3 V | 1 GHz | 14 | TQFP-100-EP (14×14) |

|

CBM99D10BQ | 1,8 V bis 3,3 V | 1 GHz | 14 | TQFP-100-EP (14×14) |

Typische Anwendungen:

Die Abbildung zeigt einen DDS-basierten frequenzvariablen Schleifenoszillator, der eine digitale Steuerung zur Erzielung hochpräziser Frequenzsignale ermöglicht. Der genaue Ablauf ist wie folgt: Der Eingang gelangt zunächst in ein 1GSPS DDS-Modul, um ein hochauflösendes Digitalsignal zu erzeugen. Anschließend wird es in zwei Kanäle aufgeteilt, von denen einer über den DAC direkt in ein analoges Signal umgewandelt und durch den DC-400 MHz Tiefpassfilter entfernt wird. Der andere Kanal wird vom Frequenzteiler erzeugt, um eine feste Schleife LO1 zu erzeugen und ein stabiles 2 GHz Lokaloszillatorsignal bereitzustellen, das die Mischgenauigkeit gewährleistet. Anschließend gelangt das Signal in die PLL-Schleife, die Frequenz wird durch einen programmierbaren Teiler (÷2/÷4) reduziert und in einem 150 MHz Phasendetektor mit der Referenzfrequenz verglichen. Das erzeugte Fehlersignal wird durch die Ladungspumpe (einstellbar von 0,5 mA bis 2 mA) und den Schleifenfilter in eine stabile Spannung umgewandelt. Der VCO wird so gesteuert, dass er ein Schwingungssignal von 2 GHz ± 150 MHz ausgibt. Das System unterstützt die Frequenzsynthese über einen weiten Bereich und geringes Phasenrauschen, indem es die hohe Auflösung von DDS mit der Stabilität der PLL kombiniert. Dadurch eignet es sich für Szenarien, in denen die Frequenzgenauigkeit entscheidend ist, wie etwa Kommunikationssysteme, Radare und Testinstrumente.

.jpg)